Digital System Design & Verification: Learn the fundamentals of designing and verifying digital systems, giving you an edge in the fast-paced technology industry.

Duration

7 Weeks

Lecture Days

Monday, Wednesday, Friday

Class Timings

9 AM – 1 PM

Seats Available

30

LEARNING OUTCOMES:

The training will enable you to:

Design Digital Circuits using Datapath and Controller paradigm.

Description of Digital Circuits and their Test benches in System Verilog.

Design of RISC-V processor

Verification and compliance testing of the designed processor.

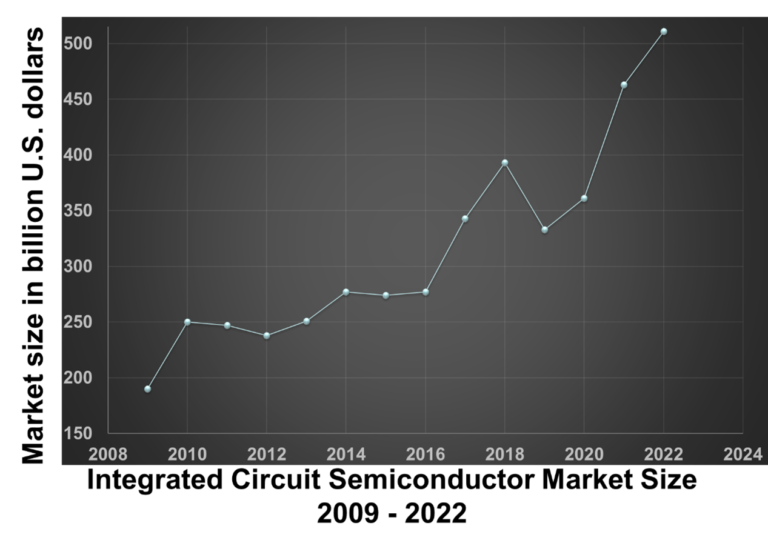

Integrated Circuit Semiconductor Market Size 2009 – 2022:

Course Outline

| 1 | Introduction | Introduction to Digital Systems Design and Verification, its job market and required softwares |

| 2 | Combinational Circuits | Introduction |

| Mux, Decoders, Encoders, Latch | ||

| RTL and Simulation | ||

| 3 | Sequential Circuits | Introduction |

| Flip flops, Counters, Shift Registers, Memory | ||

| RTL and Simulation | ||

| 4 | Datapath and Controller Paradigm | Introduction |

| State Machines, UART Transmitter | ||

| RTL and Simulation | ||

| 5 | Re-usable Testbenches | Introduction |

| Procedural blocks (initial/always) | ||

| Use of #delay | ||

| Loops (repeat, for, while) | ||

| Event control, File I/O | ||

| Writing Resusable Testbenches | ||

| 6 | Self-checking Testbenches | Introduction |

| Tasks/functions | ||

| Port & module reference | ||

| Randomization | ||

| Writing Self-checking Testbenches | ||

| 7 | RISC-V Instruction Set Architecture | Introduction |

| RISC-V (RV) Instruction Types and Formats | ||

| RISC-V Assembly Programming | ||

| Instruction Encoding Example | ||

| 8 | Writing an Assembly Program | |

| Assembly Program to Machine Code conversion | ||

| C Program to Machine Code conversion |

| 9 | RISC-V Single Cycle Processor Design | R and I type Instructions |

| Load Store Instructions | ||

| Memory Interface | ||

| 10 | RTL and Simulation | |

| Flow Control Instructions (Branch, Jump) | ||

| RTL and Simulation | ||

| 11 | RISC-V Pipelined Architecture | Introduction |

| From Single Cycle to Pipelined Architecture | ||

| 12 | Hazards | |

| RTL and Simulation | ||

| 13 | Integrating Core with Peripherals | Introduction |

| Memory Bus Interface | ||

| Integrating UART | ||

| RTL, Simulation and Testing on FPGA | ||

| 14 | Compliance Testing of designed processor | Build RISCOF environment for compliance testing |

| 15 | Build Reference Model (Sail) for compliance tests | |

| 16 | Compile riscv-arch-tests based on core configurations. | |

| Run compliance tests on riscof. |

Course Features:

Course Details:

- Certified & Experienced Instructors

- Real-Time Hands-on practice

- Build Your Own RISC-V Processor

- Conduct student Interviews with Potential Employers

- Registration Deadline: 16th July 2023

- Start Date: 17th July 2023

- Fee: 8,500 for Non-UET Students / Rs. 5,000 for UET Students

- Class Days: Monday, Wednesday, Friday

- Class Timings: 9 AM – 1 PM

Who should join this course?

EE / Mechatronics / CS / SE / CE / IT Students & Graduates

Freelancing Opportunities:

Upwork and Fiverr are the freelancing platforms which provide opportunities in this domain. A person working as a full-time freelancer can earn approximately two hundred thousand (2,00,000 PKR) monthly at the minimum for the work done in this domain which include companies’ projects and educational assignments.